## Majority Carrier Type Conversion with Floating Gates in **Carbon Nanotube Transistors**

By Woo Jong Yu, Bo Ram Kang, Il Ha Lee, Yo-Sep Min, and Young Hee Lee\*

In a conventional silicon transistor, the type of carrier is determined a priori by the dopant type. Modern electronic devices have been developed based on these fixed-polarity transistors. However, carbon nanotubes (CNTs) have shown p-type behavior under ambient conditions. [1,2] More interestingly, ambipolarity (in which the majority carrier is determined by the gate voltage) has been observed under vacuum and with a top gate oxide. [3-5] The unique ambipolarity of carbon nanotubes has been regarded as a drawback in their application to Si technology. To suppress the ambipolarity of the CNTs in CNT-based complementary metal oxide semiconductor (CMOS) technology, numerous chemical dopants such as amine-rich polymers, alkali metals, and nitronium ions, and various doping methods[6-16] have been suggested to control the majority carrier type of CNTs. The multiple gate structure has also been suggested for controlling1 the majority carrier type of CNTs but this function disappears when the voltage is not applied.<sup>[4]</sup>

On the other hand, the charge trap layer in a top-floating gate device in conventional semiconductor technology has been used to fabricate nonvolatile memory devices. CNTs have also been used for the fabrication of nonvolatile memory devices that utilize the charge trap layer.  $^{[17-27]}$  In this study, the charge trap layer in a top-floating gate was used to determine the majority carrier type of the CNT channel. Additionally, carrier-type controlled inverters were fabricated. We demonstrated that single and multilevel nonvolatile memory devices can be operated with a controllable majority carrier type. This freedom is an additional function compared to Si devices, and could open up new opportunities in designing CNT-based nanodevices for terabit integration.

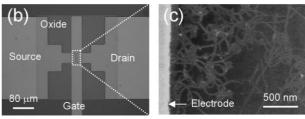

Figure 1a shows a schematic of a nonvolatile memory cell. Charges can be trapped in the trap layer through the thin tunneling oxide by the control gate. A thick layer of blocking gate was implemented to prevent charge sloshing from the control gate. The channel between the source and drain consists of randomly networked single-walled (SW)CNTs synthesized by plasma-enhanced chemical vapor deposition (PECVD; Fig. 1b and c). This device clearly showed ambipolarcurrent-gate voltage  $(I-V_G)$  characteristics over a large  $V_G$  range (Fig. 1d), having hole (a) Blocking oxide Floating gate (Trap layer) Tunneling oxide Source Drain SiO<sub>2</sub>-Si substrate

carriers at a negative gate bias and electron carriers at a positive

gate bias. Large hysteresis was also observed due to the presence

of the trap layer. The large hysteresis and ambipolarity of the

CNT-transistor provide the ability to design programmable logic

Control gate

circuits and memory cells.

Figure 1. a) Three dimensional schematic of the CNT transistor with a floating gate and control top-gate. b) Optical microscopy image of a thin film transistor (top view). c) The morphology of a random network CNT in the channel area grown directly by PECVD. d)  $I-V_G$  characteristics of CNT-TFTs demonstrating large hysteresis with voltage sweeping induced by trapped charges in the floating gate.

DOI: 10.1002/adma.200900911

Hwayang-dong, Gwangjin-gu, Seoul (Korea)

<sup>[\*]</sup> Prof. Y. H. Lee, W. J. Yu, B. R. Kang, I. H. Lee Sungkyunkwan Advanced Institute of Nanotechnology, Department of Energy Science BK21 Physics Division, Center for Nanotubes and Nanostructured Sungkyunkwan University, Suwon 440-746 (Korea) E-mail: leeyoung@skku.edu Prof. Y. Min Department of Chemical Engineering, Konkuk University

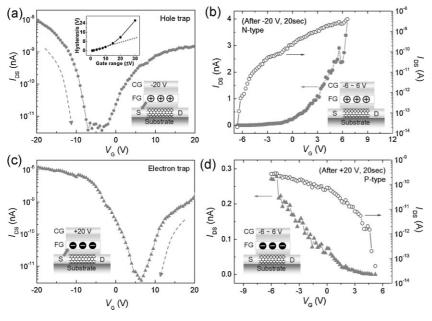

**Figure 2.** Procedure for charge trapping and the corresponding  $I-V_G$  characteristics. a) Holes were trapped in the trap layer when the voltage was swept from -20 to  $20\,\text{V}$ , and b)  $I-V_G$  characteristics after charging holes in the trap layer by applying a control gate bias at  $-20\,\text{V}$  for  $10\,\text{s}$ . c) Electrons were trapped in the trap layer when voltage was swept from  $+20\,\text{to}-20\,\text{V}$ , and d)  $I-V_G$  characteristics after charging electrons in the trap layer by applying a control gate bias at  $+20\,\text{V}$  for  $10\,\text{s}$ .

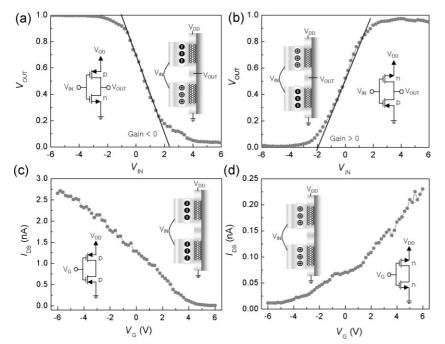

**Figure 3.** Convertible inverters with two transistors in various trapped charges. Four different types of inverter depending on the trapped charges: a) p-type transistor near  $V_{\rm DD}$ , and n-type transistor near ground, b) n-type transistor near  $V_{\rm DD}$ , and p-type transistor near ground, c) both p-type transistors, and d) both n-type transistors.

Hysteresis is typically observed in CNT transistors even without a trap layer when a back gate is present. This is attributed to the presence of ambient gases on the CNTs or between the CNTs and the gate oxide. [28-32] For low gate biases (<10 V) at which tunneling charges did not accumulate in the trap layer, hysteresis existed due to the presence of trap states at the interface between the CNTs and the tunneling oxide, as shown in the inset of Figure 2a. At a high gate bias (>10 V), the hysteresis increased exponentially with gate bias due to the charges accumulated in the trap layer. The exponential increase of hysteresis is evidence for the existence of a tunneling current through the oxide layer, where the tunneling probability is proportional to  $e^{-2\sqrt{(2m*/\hbar^2)(E_{Pb}-E)-L}}$ . Here,  $m^*$  is the effective mass of the electron,  $\hbar$  is Planck's constant,  $E_{Pb}$ is the barrier height of the oxide layer, E is the gate potential, and L is the thickness of the oxide layer.[33] Therefore, in our case, it was necessary to use a large gate bias (>10 V) to trap charges in the trap layer by tunneling.

When the gate bias was swept from -20 V to +20 V, holes were trapped in the trap layer at -20 V. causing the threshold voltage to decrease (Fig. 2a). To trap holes in the trap layer, -20 V was applied for 20 s (Fig. 2b). As a consequence, the channel showed n-type behavior in the gate bias range from -6 V to + 6 V. Because there was no charge tunneling in this gate range, the n- or p-type characteristics were retained (inset of Fig. 2a). The electron trap was created in an analogous manner (Fig. 2c). When the gate bias was swept from +20 V to -20 V, electrons were trapped in the trap layer at +20 V, increasing the threshold voltage. Thus, +20 V was applied for 20 s to accumulate electrons in the trap layer. This resulted in a p-type transistor, as shown in Figure 2d. This demonstrates that the majority carrier can be altered by the polarity of the trapped charges in the trap layer, i.e., a floating FET is created using the trap layer. The idea of a trap layer exists in Si technology, but the type conversion of the channel is an additional function of the ambipolar CNT-transistor that could be beneficial in future applications.

To confirm the type conversion of the transistors, an inverter was fabricated using two CNT-FETs. A p-type transistor using an electron trap near the supply voltage ( $V_{\rm DD}$ ), and an n-type transistor using a hole trap near ground generated typical inverter characteristics for  $V_{\rm OUT}$  (0 and 1) with  $V_{\rm IN}$  variables (Fig. 3a). In this case, a positive gain was

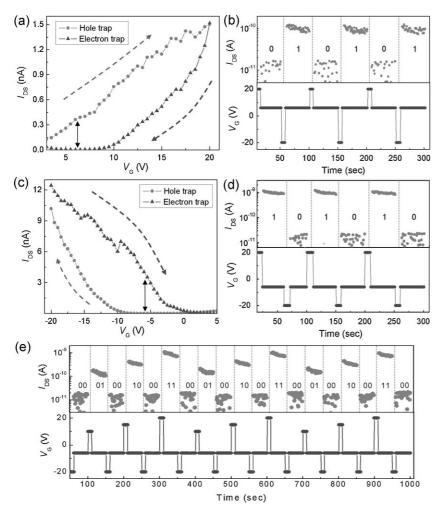

**Figure 4.** Convertible nonvolatile memory cell: a) Hysteresis curve caused by trapped charges (hole trap in top red-circle curve and electron trap in bottom green-triangle curve), and b) the corresponding (0,1) series of 1-bit cells. The majority carrier type was electrons. Data in c) and d) are analogous to (a) and (b) but the majority carrier type was holes. e) A 2-bit multilevel cell controlled by the amount of trapped charges, i.e., by the applied voltages.

obtained. On the other hand, with an n-type transistor near  $V_{\rm DD}$  and p-type transistor near ground (i.e., with type conversion), similar inverter characteristics were obtained but with positive gain polarity (Fig. 3b). In the inverter using two electron-trapped transistors, simple p-type behavior was obtained, as shown in Figure 3c. Similarly, n-type behavior was obtained using two hole-trapped transistors (Fig. 3d). We emphasize here that the inverter type can be easily converted by changing the polarity of the trapped charges in the trap layer. A convertible inverter cannot be realized in Si technology, since the majority carrier type is fixed.

We also demonstrated a convertible nonvolatile memory device using this top-floating gate CNT-FET. When electrons were trapped in the trap layer at a gate bias of  $+20 \,\mathrm{V}$ , the threshold voltage increased, as previously mentioned (Fig. 2c). In this case, the drain current ( $I_{\mathrm{DS}}$ ) at 6 V was nearly zero (Fig. 4a). When holes were trapped at a gate bias of  $-20 \,\mathrm{V}$ , the threshold voltage decreased and  $I_{\mathrm{DS}}$  at a read voltage of 6 V was high. At a gate bias of  $+6 \,\mathrm{V}$ , the majority carriers in the CNT channel were electrons,

thus the (0,1) 1-bit was repeated, as shown in Figure 4b. If the memory bit was operated at a read voltage of  $-6 \,\mathrm{V}$ , the (1,0) 1-bit was repeated in reverse (Fig. 4c and d). The majority carriers were holes in this case. The (0,1) or (1,0) 1-bit together with the majority carrier type could be controlled by the polarity of the trapped charges. A 2-bit multilevel nonvolatile memory cell could also be constructed, as shown in Figure 4e. At a gate bias of -20 V, holes were trapped, and no current flowed at -6 V. At a gate bias of 10 V, a hole current flowed at  $-6 \, \text{V}$ . With increasing gate bias, the hole current also increased at -6 V. The current magnitudes at gate biases of 10, 15, and 20 V were clearly distinguished from each other. This was repeatable with many cycles. Thus, 2-bit memory was demonstrated with hole carriers.

In summary, type conversion of the CNT channel was realized by controlling the charge polarity in the top trap layer. Although the idea of a trap layer exists in Si technology, the operation of a CNT transistor provided more freedom in determining the majority carrier of the channel. We were able to demonstrate a convertible inverter, that gain polarity could be changed, and a nonvolatile memory device using the floating CNT-FET. This offers possibilities for designing CNT based CMOS logic circuits.

## Experimental

An array of thin film transistors (TFTs) was fabricated with randomly networked SWCNTs that were selectively synthesized on an array of catalyst photoresists (0.01 M of ferrocene) [34] using remote plasma-enhanced chemical vapor deposition (PECVD)

at a low temperature (450 °C) [35]. The corresponding source and drain electrodes composed of Ti (5 nm)/Au (50 nm) (channel lengths: 2, 3, 5, 7, 10  $\mu$ m; width: 40  $\mu$ m, 20 channels for each length in the sample) were deposited to form an array of 200 TFTs. A thin film of top-gate tunneling oxide (Al<sub>2</sub>O<sub>3</sub>, 5 nm)-metal trap layer (7 nm)-blocking oxide (Al<sub>2</sub>O<sub>3</sub>, 50 nm) was deposited by atomic layer deposition at 150 °C. The gate electrode (Ti (5 nm)/Au (50 nm)) was formed similarly to the source and drain electrodes. The yield of transistors with on/off ratio of greater than 10<sup>4</sup> was 88% [5]. The detailed method has been described elsewhere [34,35]. Logic circuits were fabricated by connecting several TFTs with gold wire using wire bonder. The I-V characteristics of the CNT-TFTs were measured under ambient conditions by a source-measure unit (Keithley 236, 237) using a probe station. Scanning electron microscope (JEOL, JSM-7401F) images were taken in secondary electron image mode under a pressure of  $\sim 4 \times 10^{-3} \, \mathrm{Torr}$  (1Torr  $\sim 133.3 \, \mathrm{Pa}$ ).

## Acknowledgements

This work was supported by the MOEST through the STAR-faculty project, TND project, WCU (World Class University) program through the KOSEF

funded by the MOST (R31-2008-000-10029-0), the KICOS through a grant provided by MOST in 2007 (No. 2007-00202), and KOSEF through CNNC at SKKU.

Received: March 16, 2009 Revised: June 15, 2009 Published online: August 12, 2009

- [1] S. J. Tans, A. R. M. Verschueren, C. Dekker, Science 1998, 393, 49.

- [2] R. Martel, T. Schmidt, H. R. Shea, T. Hertel, P. Avouris, Appl. Phys. Lett. 1998. 73, 2447.

- [3] R. Martel, V. Derycke, C. Lavoie, J. Appenzeller, K. K. Chan, J. Tersoff, P. Avouris, Phys. Rev. Lett. 2000, 87, 256805.

- [4] S. Koo, Q. L. Monica, D. Edelstein, C. A. Richter, E. M. Vogel, Nano Lett. 2005. 5, 2519.

- [5] W. J. Yu, U. J. Kim, B. R. Kang, I. H. Lee, E. H. Lee, Y. H. Lee, Nano Lett. 2009, 9, 1401.

- [6] S. H. Hur, C. Kocabas, A. Gaur, O. O. Park, M. Shim, J. A. Rogers, J. Appl. Phys. 2005, 98, 114302.

- [7] D. L. Carroll, P. Redlich, X. Blase, J. C. Charlier, S. Curran, P. M. Ajayan, S. Roth, M. Rühle, *Phys. Rev. Lett.* **1998**, *81*, 2332.

- [8] V. Derycke, R. Martel, J. Appenzeller, P. Avouris, Appl. Phys. Lett. 2002, 80,

- [9] R. Martel, V. Derycke, C. Lavoie, J. Appenzeller, K. K. Chan, J. Tersoff, P. Avouris, Phys. Rev. Lett. 2001, 87, 256805.

- [10] C. Klinke, J. Chen, A. Afzali, P. Avouris, Nano Lett. 2005, 5, 555.

- [11] G. P. Siddons, D. Merchin, J. H. Back, J. K. Jeong, M. Shim, Nano Lett. 2004, 4, 927.

- [12] K. H. An, Y. H. Lee, NANO 2006, 1, 115.

- [13] W. J. Yu, S. Y. Jeong, K. K. Kim, B. R. Kang, D. J. Bae, M. Lee, S. Hong, S. P. Gaunkar, D. Pribat, D. Perello, M. Yun, J. Y. Choi, Y. H. Lee, *New J. Phys.* 2008, *10*, 113013.

- [14] B. R. Kang, W. J. Yu, K. K. Kim, H. K. Park, S. M. Kim, Y. Park, G. Kim, H. J. Shin, U. J. Kim, E. H. Lee, J. Y. Choi, Y. H. Lee, Adv. Funct. Mater. 2009, 19, DOI: 10.1002/adfm.200801712

- [15] S. M. Kim, J. H. Jang, K. K. Kim, H. K. Park, J. J. Bae, W. J. Yu, I. H. Lee, G. Kim, D. D. Loc, U. J. Kim, E. H. Lee, H. J. Shin, J. Y. Choi, Y. H. Lee, J. Am. Chem. Soc. 2009, 131, 327.

- [16] V. Derycke, R. Martel, J. Appenzeller, P. Avouris, Nano Lett. 2001, 1, 453.

- [17] A. Gruneis, M. J. Esplandiu, D. Garcia-Sanchez, A. Bachtold, Nano Lett. 2007, 7, 3766.

- [18] T. Rueckes, K. Kim, E. Joselevich, G. Y. Tseng, C. L. Cheung, C. M. Lieber, Science 2000, 289, 94.

- [19] M. S. Fuhrer, B. M. Kim, T. Durkop, T. Britlinger, Nano Lett. 2002, 2, 755.

- [20] M. Radosavljevic, M. Freitag, K. V. Thadani, A. T. Johnson, Nano Lett. 2002, 2, 761.

- [21] J. B. Cui, R. Sordan, M. Burghard, K. Kern, Appl. Phys. Lett. 2002, 81, 3260.

- [22] W. B. Choi, S. Chae, E. Bae, J. W. Lee, B. H. Cheong, J. R. Kim, J. J. Kim, Appl. Phys. Lett. 2003, 82, 275.

- [23] L. Marty, V. Bouchiat, C. Naud, M. Chaumont, T. Fournier, A. M. Bonnot, Nano Lett. 2003, 3, 1115.

- [24] S. Wang, P. Sellin, Appl. Phys. Lett. 2005, 87, 133117.

- [25] U. Ganguly, E. C. Kan, Y. Zhangb, Appl. Phys. Lett. 2005, 87, 043108.

- [26] M. Rinkio, A. Johansson, M. Y. Zavodchikova, J. J. Toppari, A. G. Nasibulin, E. I. Kauppinen, P. Torma, New J. Phys. 2008, 10, 103019.

- [27] M. Rinkio, A. Johansson, G. S. Paraoanu, P. Torma, Nano Lett. 2009, 9, 643

- [28] W. Kim, A. Javey, O. Vermesh, Q. Wang, Y. Li, H. Dai, Nano Lett. 2003, 3, 193.

- [29] J. S. Lee, S. Ryu, K. Yoo, I. S. Choi, W. S. Yun, J. Kim, J. Phys. Chem. C 2007, 111, 12504.

- [30] A. Vijayaraghavan, S. Kara, C. Soldano, S. Talapatra, O. Nalamasu, P. M. Ajayan, Appl. Phys. Lett. 2006, 89, 162108.

- [31] M. Radosavljevi, M. Freitag, K. V. Thadani, A. T. Johnson, Nano Lett. 2002, 2, 761.

- [32] J. B. Cui, R. Sordan, M. Burghard, K. Kern, Appl. Phys. Lett. 2002, 81, 3260.

- [33] B. L. Anderson, R. L. Anderson, Fundamentals of Semiconductor Devices, McGraw-Hill, New York 2005.

- [34] Y. Min, E. J. Bae, J. B. Park, W. Park, Nanotechnology 2006, 17, 116.

- [35] Y. S. Min, E. J. Bae, B. S. Oh, D. Kang, W. Park, J. Am. Chem. Soc. 2005, 127,